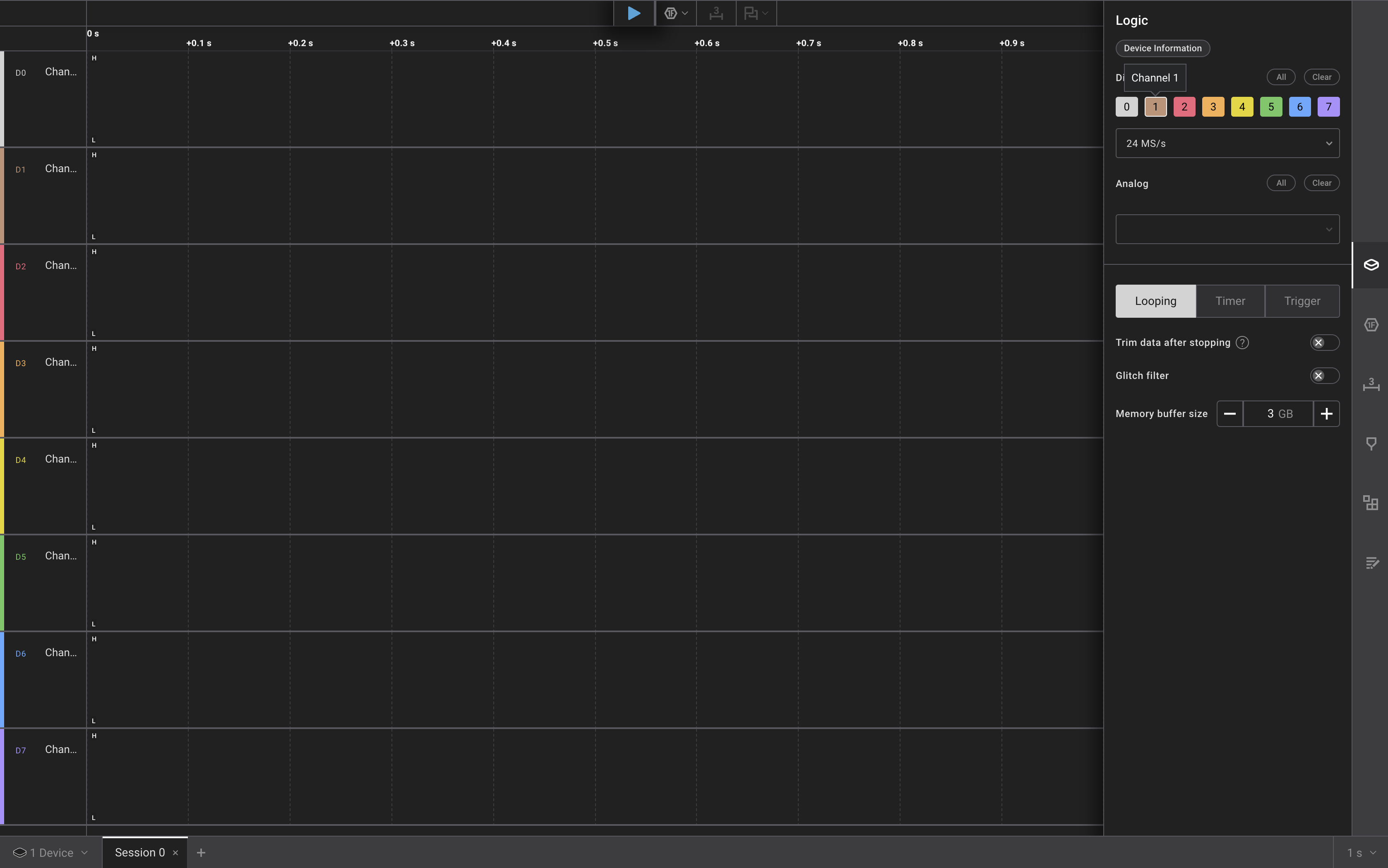

This group assignment was about understanding how a microcontroller board behaves electrically, not only that the code "runs." At the most basic level, a microcontroller communicates with the outside world by changing voltage over time. If we can observe those voltage changes, we can verify timing, protocol behavior, and signal quality.

A logic analyzer is best when the signal is digital and protocol-based. It samples high/low states and lets us decode communication buses such as I2C.

So this test answers: is the microcontroller generating valid I2C traffic with consistent timing?

0x3CD7 toggled each transmission for timing correlation

This NAK is expected in our setup because we intentionally tested on an empty bus (no slave connected). The microcontroller still generated valid I2C timing and addressing, which is exactly what we wanted to verify at this stage.

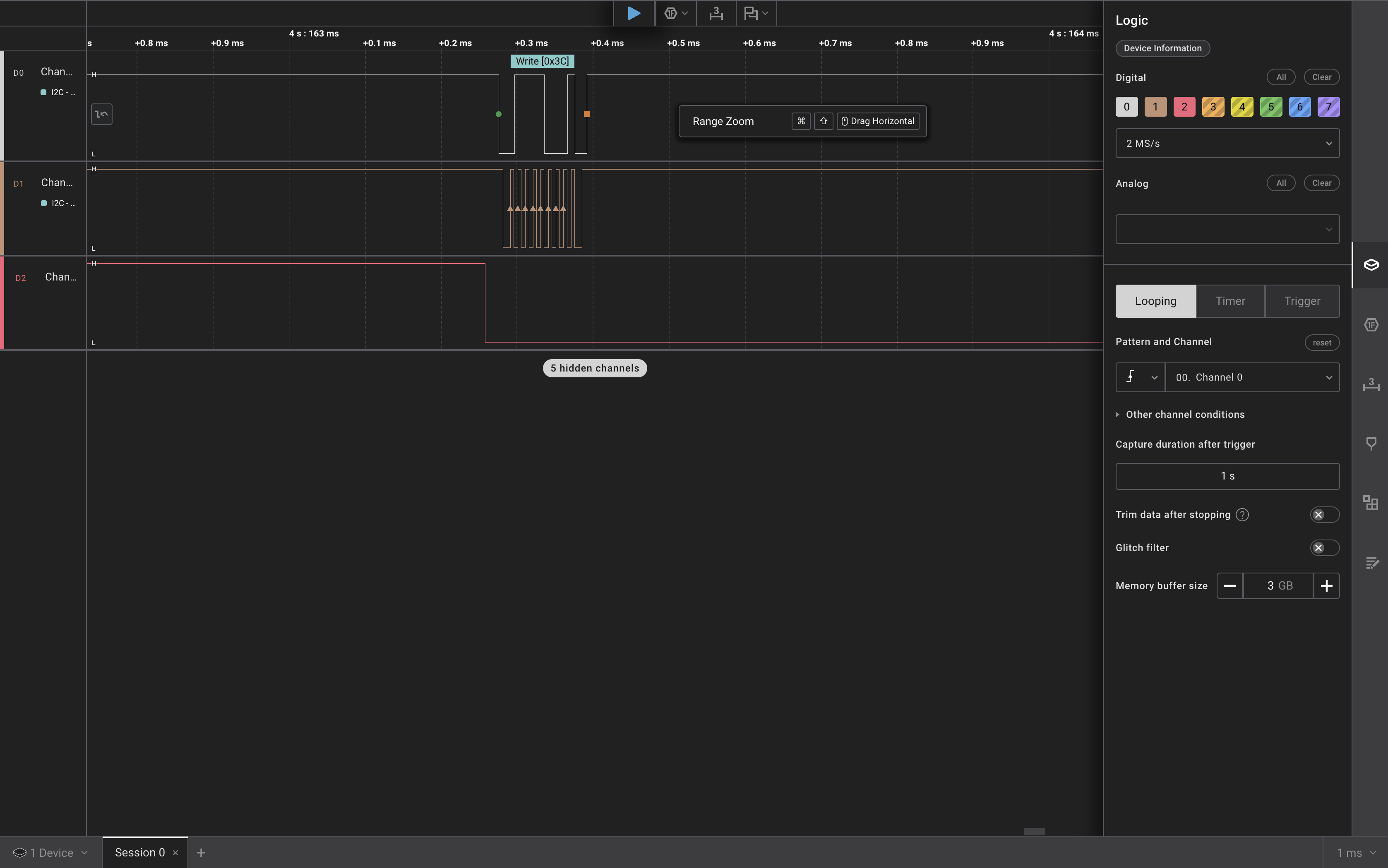

An oscilloscope lets us inspect the analog shape of voltage vs time. For PWM, that is important because PWM is fundamentally a time-domain signal:

So this test answers: is the board producing a stable PWM waveform, and does the duty-cycle change behave as expected?

We used a simple PWM ramp on Uno pin D9:

analogWrite(9, x)

x increments every 250 ms

resets after 255This creates a duty-cycle sweep from ~0% to ~100%, repeating continuously.

The oscilloscope test confirmed that the microcontroller output timing is stable and that PWM control is behaving correctly.