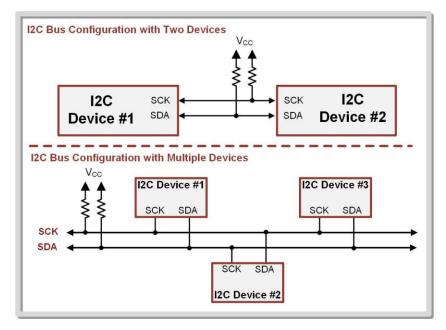

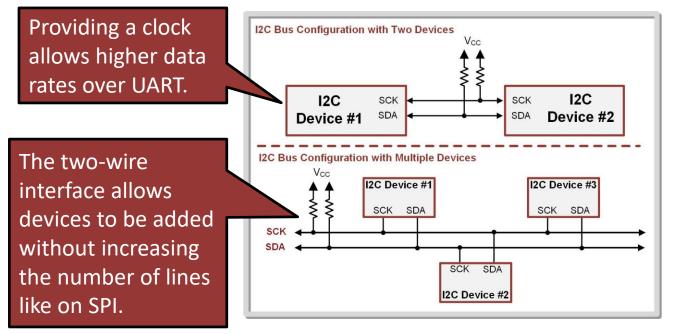

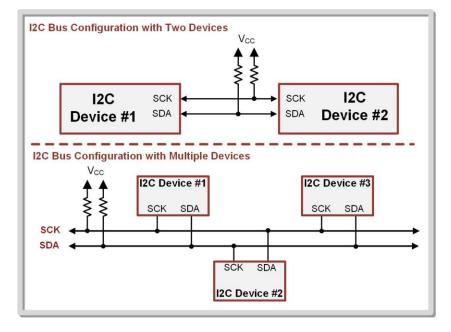

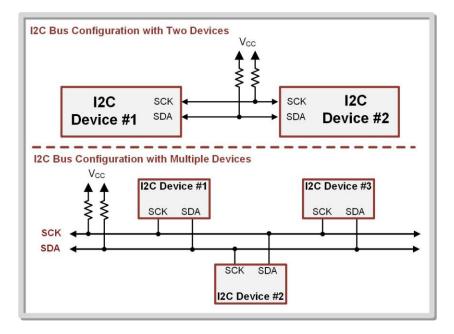

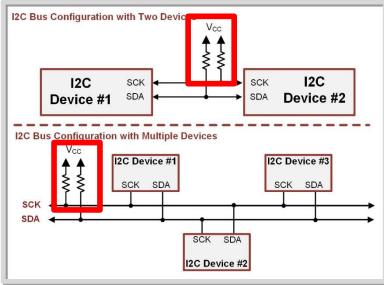

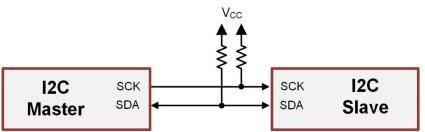

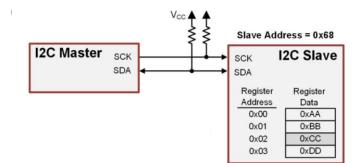

The Inter-Integrated Circuit (I2C) standard is a serial interface implement with a two-wire link that can support multiple masters and multiple slaves.

The Inter-Integrated Circuit (I2C) standard is a serial interface implement with a two-wire link that can support multiple masters and multiple slaves.

The Inter-Integrated Circuit (I2C) standard is a serial interface implement with a two-wire link that can support multiple masters and multiple slaves.

### 14.3.1 THE I2C PROTOCOL

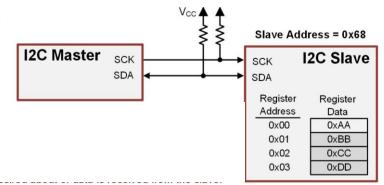

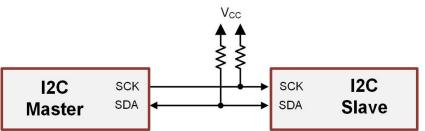

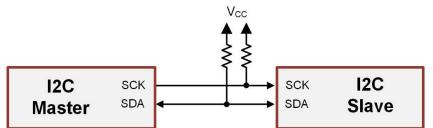

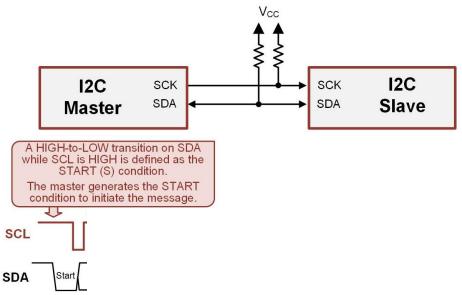

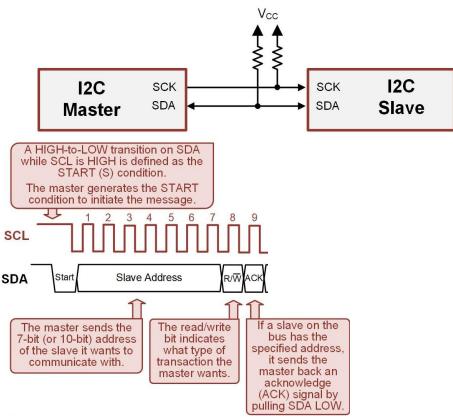

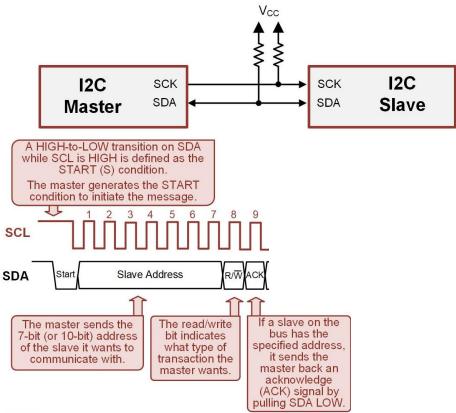

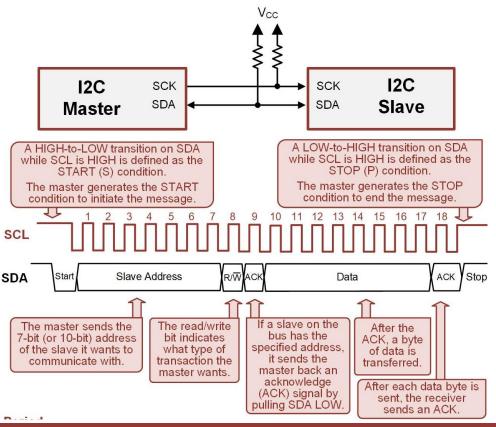

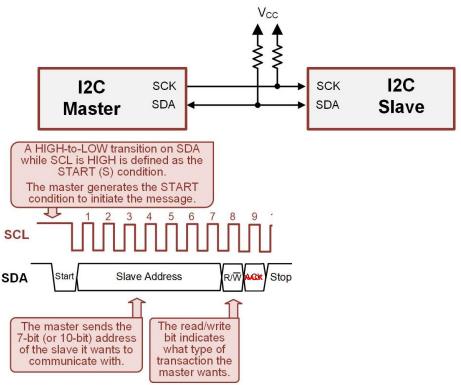

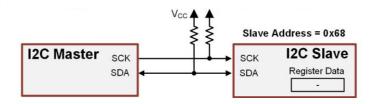

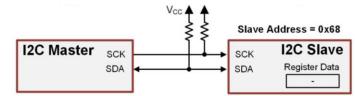

• An I2C bus contains a clock line (SCK) and data line (SDA).

• An I2C link is always **half-duplex**, meaning that all devices share the data line with only one device transmitting at any given time.

- An I2C bus ALWAYS needs external pull-up resistors on each of its lines.

- These can't be implemented on the MCU because the resistor function is only available when the port is configured as an INPUT.

- Since I2C is bidirectional, we never know wither the pin will be an input or output.

Master – the device that initiates communication and controls the clock.

Multiple masters are also supported on an I2C bus.

- Slave a device on the bus that is read or written to, but does not initiate transmission or provide a clock.

- Slave address a unique and <u>predetermined</u> address for each slave on the bus.

- This address is used by the master to indicate which slave it wants to communicate with.

- Idle when both SDA and SCL are held high by the pull-up resistors and no I2C device is attempting to communicate.

- Busy when devices are driving the bus.

sda

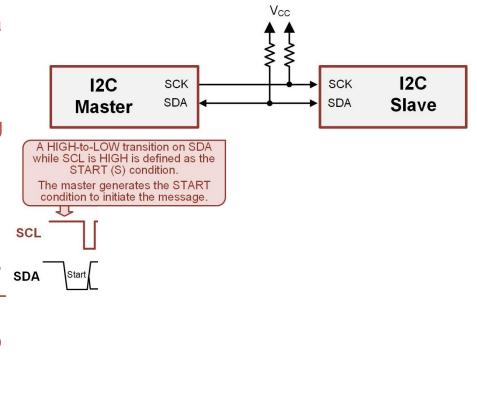

- **Messages** how I2C information is transferred.

- A master initiates a new message by generating a START (S) condition by pulling SDA LOW while SCL is still HIGH.

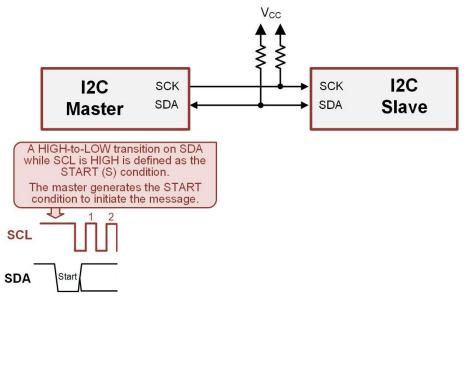

- As soon as the START condition is generated, the SCL will be pulled LOW and start pulsing to provide the clock for the message.

The master is responsible for pulsing the clock.

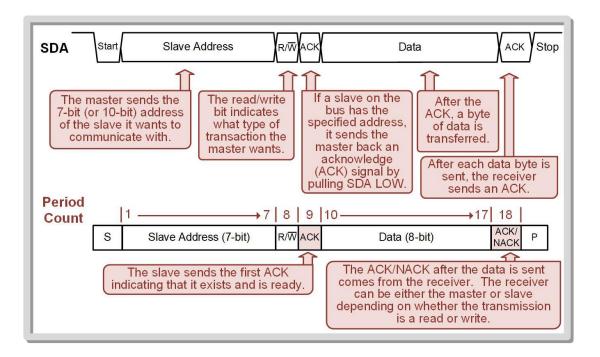

- Each clock pulse within the I2C message is numbered by periods.

- Both the master and the slaves count the number of periods that have occurred since the message started in order to know when certain frames and signals should be present.

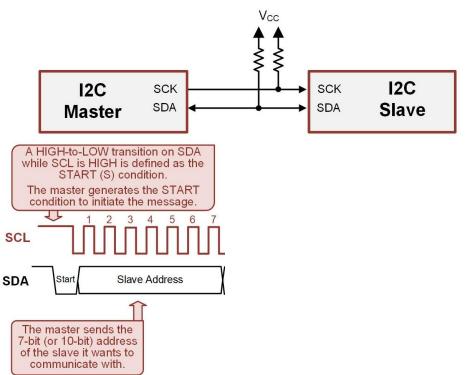

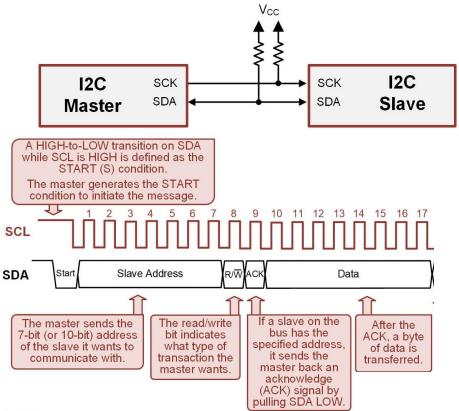

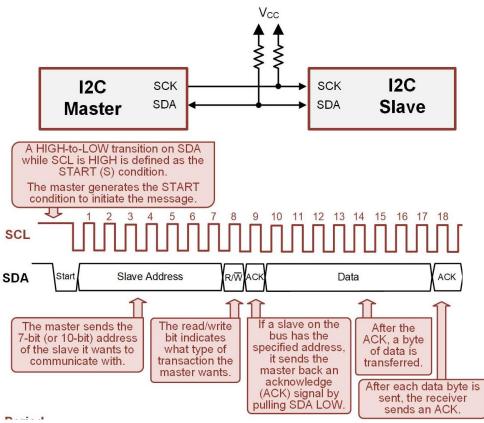

After the master generates the START condition, it first sends the slave address that it wishes to communicate with.

I2C slave addresses can either be 7-bit (default) or 10-bit.

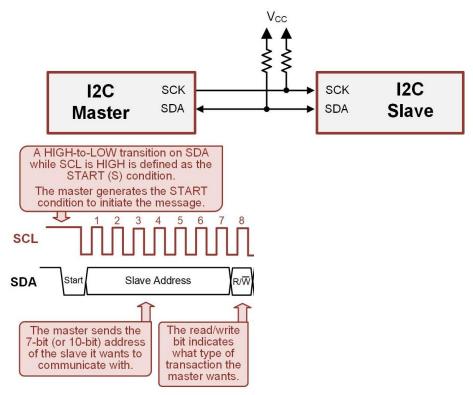

- The slave address is followed by the read/write signal indicating which type of transaction is being requested in the message.

- The START condition, slave address, and read/write signal constitute periods 1 → 8.

- Period 9 of the message is reserved for the slave acknowledge (ACK) or noacknowledge (NACK) signal.

- After the slave address and read/write signal are sent by the master, each slave on the bus checks whether it is being addressed.

- If a slave exists with the specified slave address, it will send an ACK signal back to the master by pulling SDA LOW.

- If no device exists with the specified slave address, no device will pull down<sub>SDA</sub> SDA. This will result in period 9 remaining HIGH anc will be interpreted as a NACK.

If the master sees the ACK signal, it knows a slave exists with the specified address and proceeds with the message.

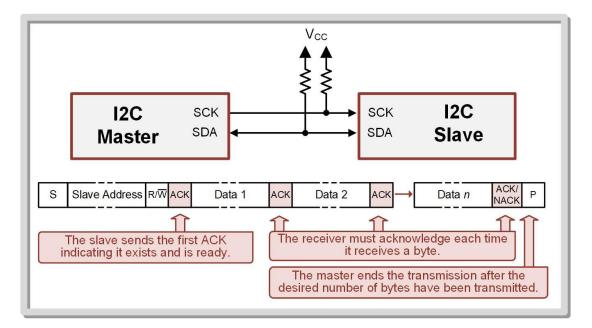

After each byte is sent, the receiving device sends an ACK signal indicating that it successfully received the data.

- A STOP condition occurs when there is a LOW-to-HIGH transition on SDA while SCL is HIGH.

- Once, SDA goes HIGH, SCL also remains HIGH indicating that the bus is idle again.

mante d

- A NACK in period 9 tells the master that no slave exists with the specified address.

- The master then generates a STOP condition and ends the message.

- When the master is **writing** to a slave, the master sends the 8-bits of data and the slave produces the ACK/NACK signal.

- When the master is **reading** from a slave, the slave sends the 8-bits of data and the master produces the ACK/NACK signal.

- After the data has been sent and acknowledged, the master can end the message by generating the STOP condition anytime.

### 14.3.1 THE I2C PROTOCOL

• The Master can send multiple data bytes in a single message.

# 14.3.1 THE I2C PROTOCOL

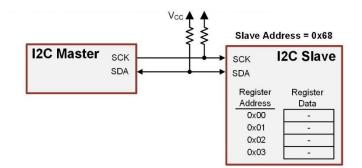

I2C devices contain individual registers that hold their information.

In the simplest case, an I2C device contains only a single register.

# 14.3.1 THE I2C PROTOCOL

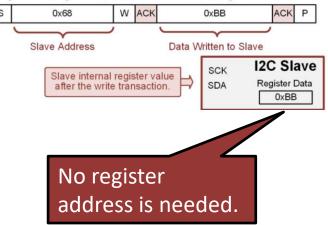

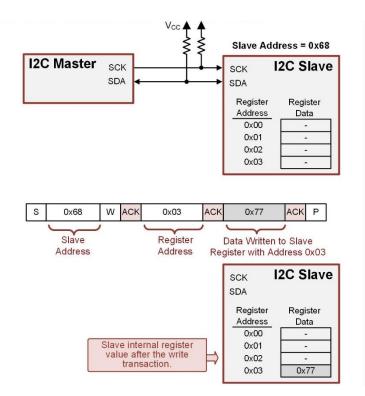

- <u>Writing</u> to a slave with a single register.

- The master initiates the message by sending the S bit.

- The master provides the slave address and a WRITE signal.

- The slave ACKs to indicate it is ready.

- The master writes the data.

- The slave sends an ACK that it got the data.

- The master ends the message by sending the P bit.

Write Example – The master sends the slave address and pulls SDA LOW to indicate a write transaction. The next byte sent by the master is stored into the slave's register. During a write, the slave sends the ACK signal.

# 14.3.1 THE I2C PROTOCOL

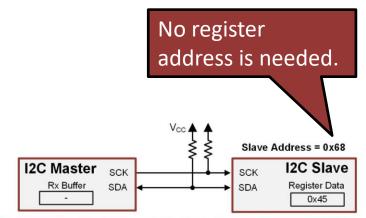

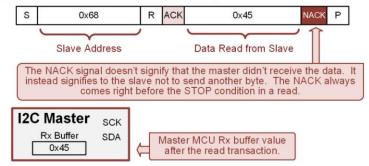

- <u>**Reading**</u> from a slave with a single register.

- The master initiates the message by sending the S bit.

- The master provides the slave address and a WRITE signal.

- The slave ACKs to indicate it is ready.

- The slave sends the data.

- The master sends a NACK to stop the slave from sending more data.

- The master ends the message by sending the P bit.

**Read Example** – The master sends the slave address and leaves SDA HIGH to indicate a read transaction. The slave then sends a byte of data to the master. If the byte received is the last byte that the master wants, the master sends a NACK signal followed by the STOP condition to end the message.

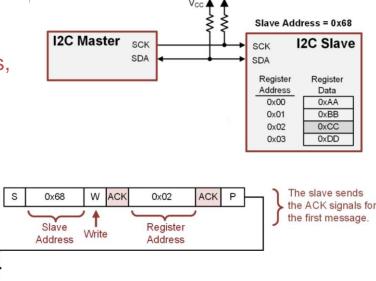

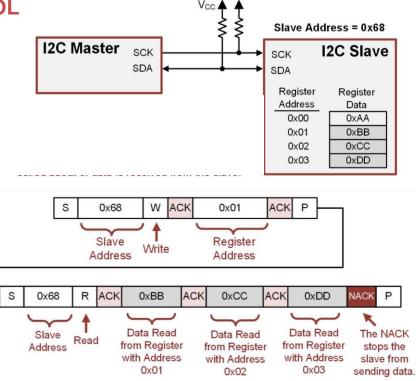

- When an I2C device has multiple registers, each is assigned a register address.

- To access a specific register in the slave, the master needs to provide the register address in the message.

- For a <u>write</u> transaction, the master generates an I2C message that first provides the slave address, then provides the register address to access, then provides the data to be written.

- After each frame, the slave sends an ACK signal.

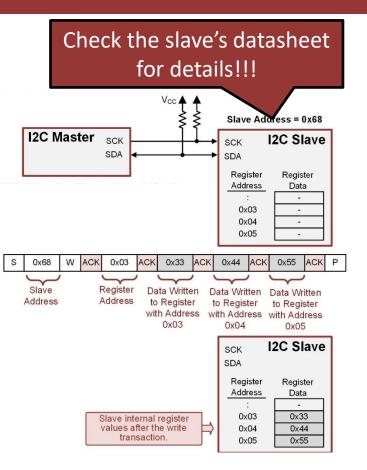

- The master can also <u>write</u> a block of data to registers.

- The slave automatically increments the starting address after each byte of data is written.

- The master still sends the slave address, the write signal, and the starting register address.

- The next byte of data that is sent goes into the first register address location.

## 14.3.1 THE I2C PROTOCOL

The slave will continue to increment its register address until it sees the STOP condition generated by the master.

### 14.3.1 THE I2C PROTOCOL

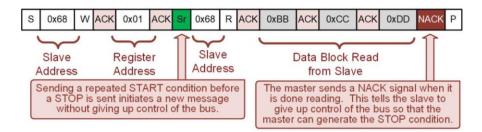

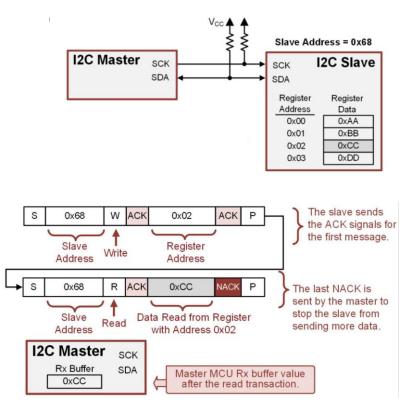

• When <u>reading</u> from a device that contains multiple registers, two message are needed.

- When <u>reading</u> from a device that contains multiple registers, two message are needed.

- The first message sets the register address within the slave that will be read from using a write transaction.

- The first message puts the slave into a mode where it's expecting a second message that will read data from the register address that was just sent.

## 14.3.1 THE I2C PROTOCOL

• The second message performs a read transaction that retrieves the data from the register address sent in the first message.

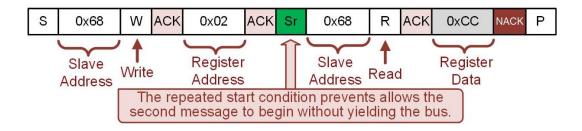

- An alternative approach can also be used where a second START (Sr) condition is generated before the STOP condition of the first message.

- This initiates the second read transaction immediately without giving up control of the bus.

- The master can also <u>read</u> blocks of data from a slave.

- In this situation, the master still sends two messages, the first setting the register address and the second retrieving the data.

- In the second message, the master continually sends SCL pulses to rea as many bytes as it want prior to generating the STOP condition.

## 14.3.1 THE I2C PROTOCOL

A repeated Start bit (Sr) can also be used to read blocks of information.