Week 9

Getting started with Embedded Programming

This weeks assignment was to read a microcontroller datasheet and program my board to do something using as many environments ..........

So before starting to program my board I have to do some background work ..... as I was on MAC so I need to install FTDI drivers to interface the board with the computer..... I followed this link to install the drivers..... So now I was all set to program the board..... I decided to program my board using Arduino IDE at first then move ahead with other platforms ....... as its community is very large and all sort of support can be found online.

ATTINY 44

To have a better understanding of the Microcontroller, best way is to go through its Data Sheet.

You can download Data Sheet from here.

Image Ref : LINK

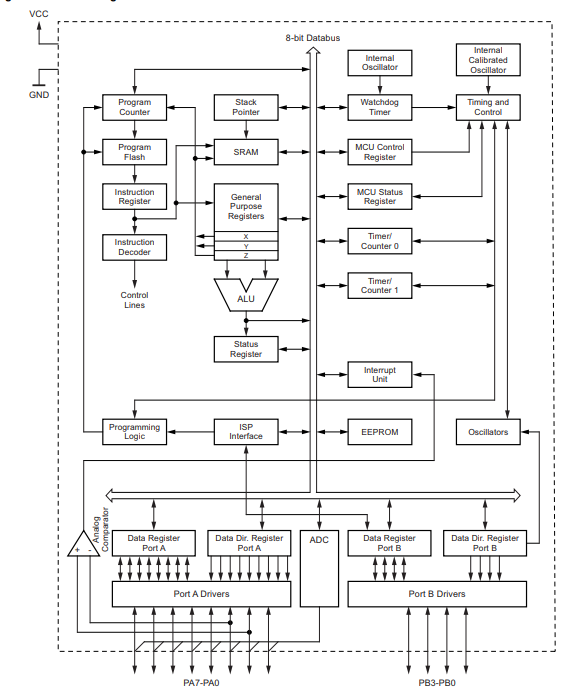

ATTINY 44 is a low power AVR 8 Bit RISC Based Microcontroller.

Overveiw from Datasheet

>Program Memory Type : Flash

>Program Memory : 4KB

>CPU Speed : 20 MIPS

>RAM Bytes : 256

>DATA EEPROM Bytes : 256

>Digital Communication : 1SPI , 1 I2C

>Capture/ Compare / PWM Peripherals : 1 Input Capture, 1CCP, 4 PWM

>Timers : 1 x 8bit, 1 x 16bit

>Comparators : 1

>Temperature Range : -40 to 85

>Operating Voltage : 1.8 to 5.5V

>Pin Count : 14

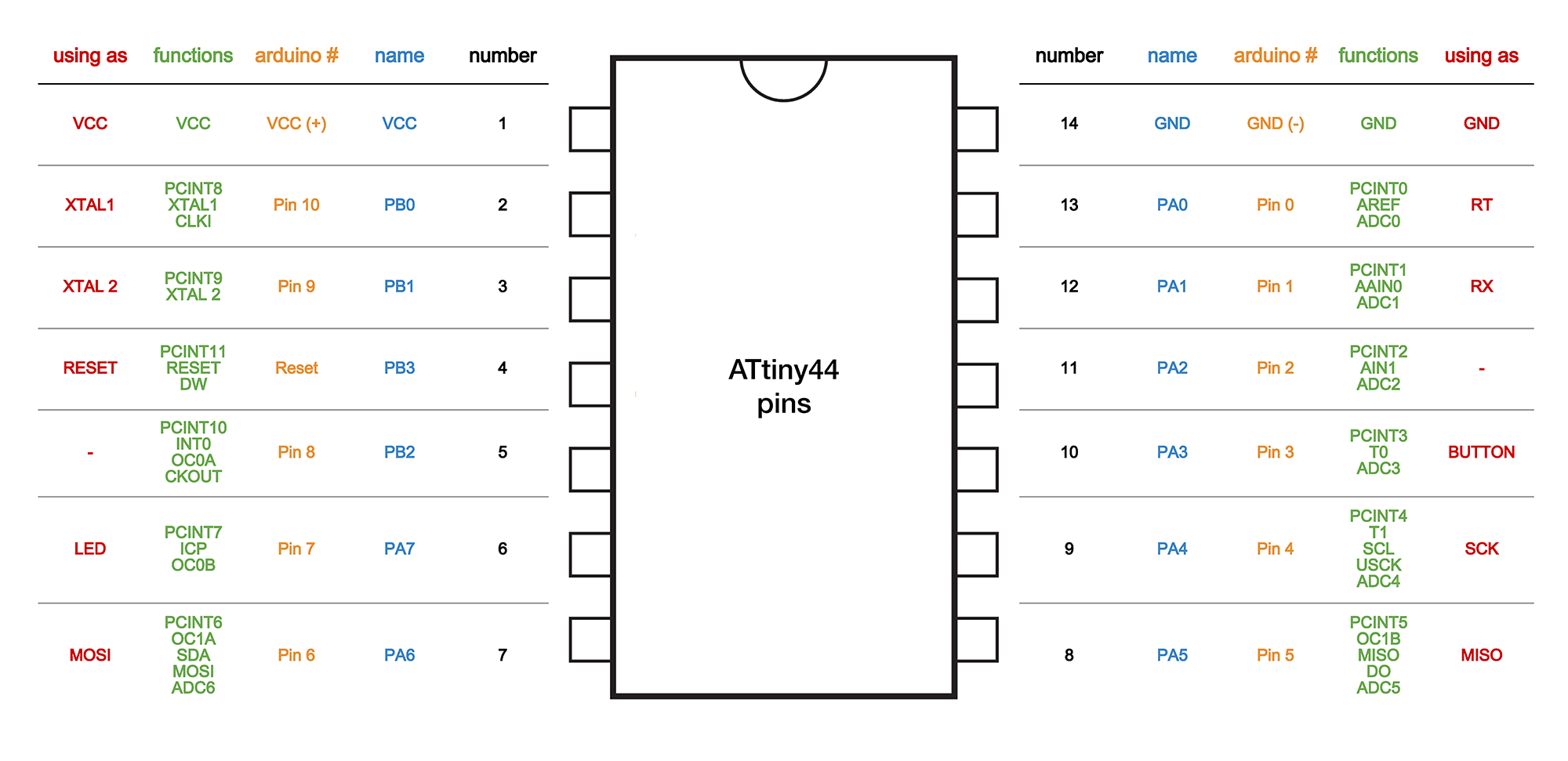

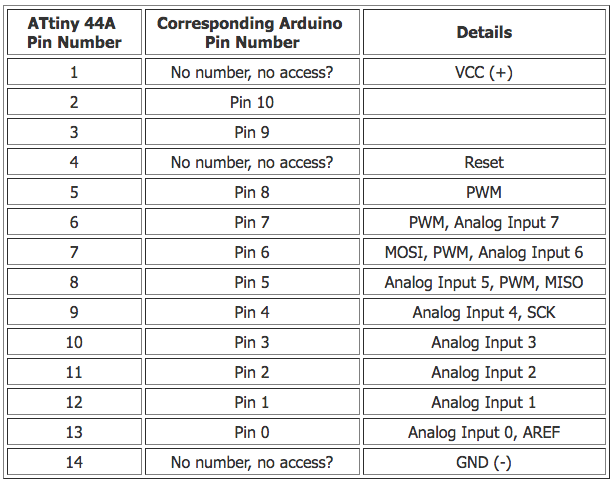

Pin Description

>VCC : Input Voltage

>GND : Ground

>RESET : Reset input. Low Level ( GND ) on this pin will reset the program.

>Port B (PB3...PB0) : Port B is a 4-bit bi-directional I/O port with internal pull-up resistors (selected for each bit).

>Port A (PA7...PA0) :Port A is a 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit).

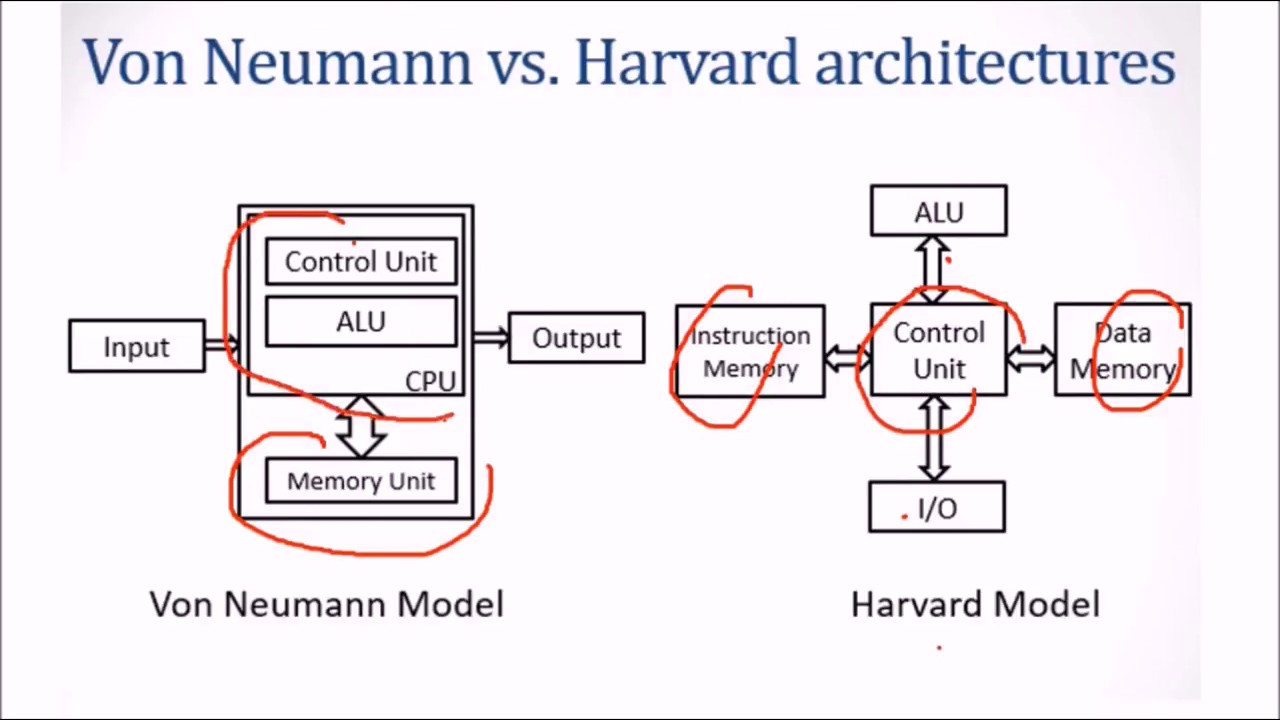

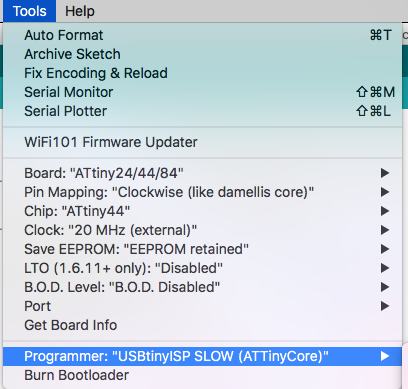

Block Diagram

Block diagram's are not as much important as understanding the pins, Block diagram is more of an internal thing, It explains how things

are going on inside the Microcontroller, ATTINY 44 follow Harvard Architecture . It has seperate Buses and Memories for program and

data.

Block diagram's are not as much important as understanding the pins, Block diagram is more of an internal thing, It explains how things

are going on inside the Microcontroller, ATTINY 44 follow Harvard Architecture . It has seperate Buses and Memories for program and

data.

Programming Pins

SCK(Serial Clock): Programming clock, generated by the In-System Programmer (Master) (Master Out - Slave In ): Communication line from In-System Programmer (Master) to target AVR being programmed (Slave ) MISO( Master In - Slave Out ): Communication line from target AVR (Slave) to In- System Programmer (Master) RST(Reset): To enable In-System Programming, the target AVR Reset must be kept active. To simplify this, the In-System Programmer should control the target AVR Reset GND(Ground): Common Ground VCC(+5V): +5V input

Getting started with Arduino IDE

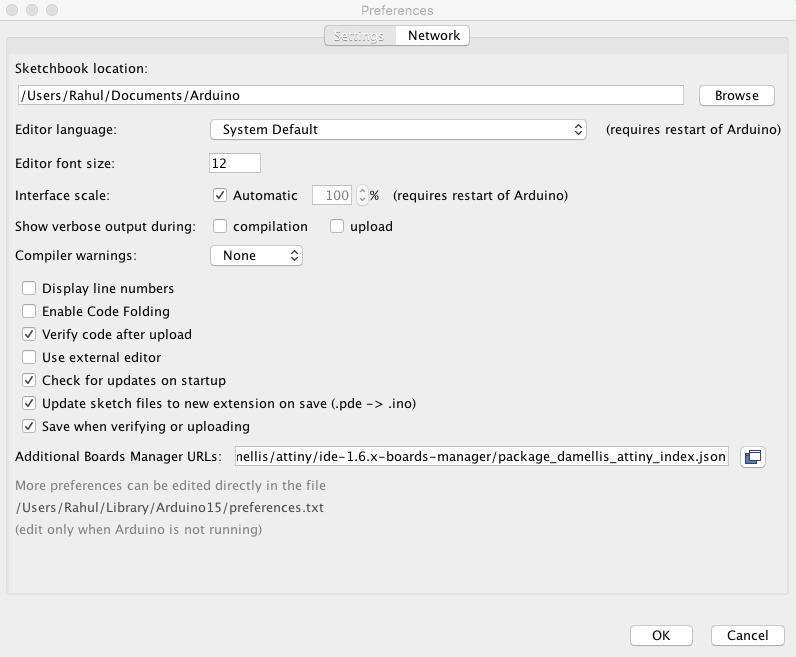

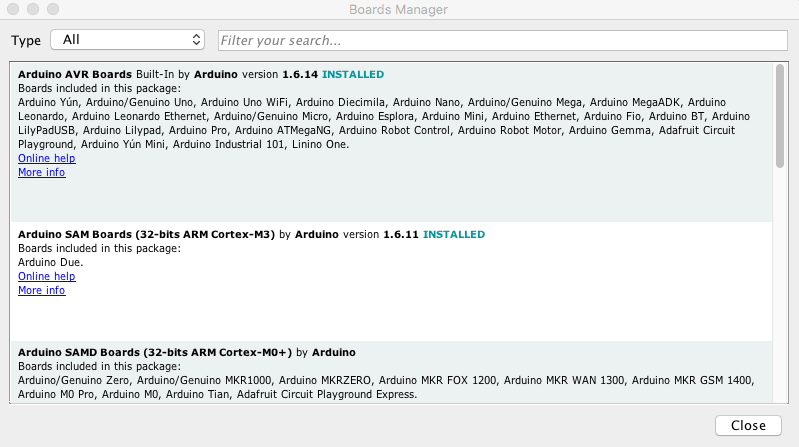

Before starting to program our board using Arduino IDE, we need to tell the software that we'll be using a thrid party hardware i.e AVR ATTINY 44/45 etc........ For this we need to go to the Board Manager and add additional boards.....

Steps to add additional boards

1. Go to Arduino Preferances and there in the text field add a link https://raw.githubusercontent.com/damellis/attiny/ide-1.6.x-boards-manager/package_damellis_attiny_index.json then click ok

2. Then go to the boards manager and install new board files as required

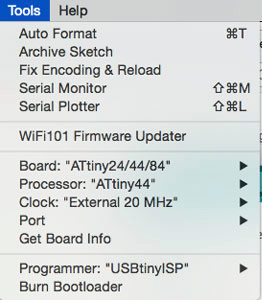

3. Now goto tools then to Boards and select the Microcontroller which you are using, in my case it was attiny 44 with 20Mhz external clock and programmer as USBTINY.

4. After this we need to burn the bootloader onto the chip, this step sets the fuses and flashes any previous configration over the chip.

Now, all set to write the program and dump it onto the chip

But before doing that we should always read the data sheet of the chip we are using ....... or atleast you should know the pin diagram of the chip you are using .....

Programming

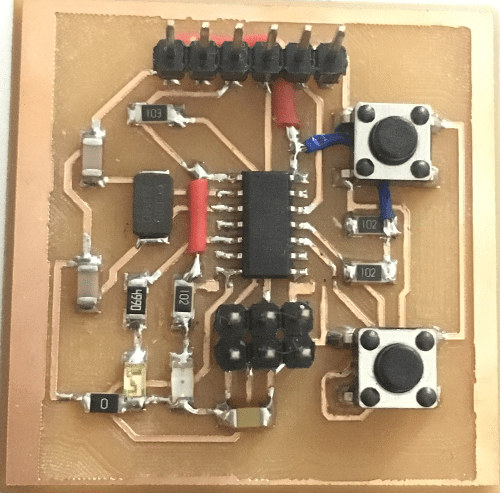

This weeks assignment was to program our board to make it do something ...... My board was having 2 Push buttons and one LED..... So I decided to program it in a way that pushing those 2 buttons would be changing the time period of the blinking of the LED.....

1. It would be declaring the variables and configuring the pins as input outputs

"A" Here is the initial delay of the LED Blinking. In the Setup I have defined the nature of the Pins Pin 8 > Output Pin, Pin 2 & 3 > Input pin

2. Now step 2 would be making the main code into the loop

This is the main loop of the program which would be running over and over. In this main loop I am comparing the Digital State of the Pin 2 & 3, If Pin 2 is HIGH then the blink interval will increment with + 20ms and maximun upto 5000ms(5seconds). If Pin 3 is HIGH then the blink interval will decrement with -20ms and can reduce to minimum 100ms. And at the end this delay paramter "A" is passed in the delay function which would be controlling the blinking with varied delay. Note: I have used Pull down method for switches, i.e I have considered HIGH Input signal as button click. I have added a pull down resistor to make sure any floating voltage value does not reaches the Pin, otherwise the controller would consider it as a button click, Also it may be noted that while programming we need to check wether the pin state is HIGH or not, If I had used Pull Up approach then we would have been checking wether the pin state is LOW or not.

Now burning the code to the chip

For programming we need to connect the board using AVR ISP cable to FABISP Programmer, The connections are shown in the video below :

Here are the steps which you need to follow to program the board

Step 1 : Write the program which I have already done

Step 2 : Burn the bootloader*, which also I have done already

About Boot Loader

Boot Loader is basically OS ( Operating system ) for the micro controllers, Bootloaders are meant to enrich the capabilities of the microcontroller and provide access to the hardware features such as USB, USART, SPI, I2C etc. The first thing which is processed by the microcontroller when it is powered on is the Boot Loader, then the boot loader instructs the controller, from where to start executing instructions. Mostly the bootloader resides in the bottom most area of the ROM but there are some cases where the boot loader can be configured in the top.The starting and ending address of the bootloader in the ROM depends on the product. So it’s recommended to use the datasheet to collect the required information.

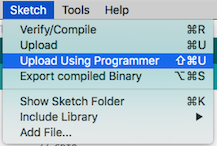

Step 3 : Go to Sketch Button over the tool bar and Click on Upload Using Programmer

Points to be noted

1. We need to power the chip externally, in my case a used +5v from arduino

2. Orientation of AVR ISP header should be correct else the program wont burn

3. Setting which should be used while programming with FABISP

Testing

Learning from data sheet

After going through the data sheet ...... I was able to understand the pin diagram of the controller.....well, it was a very long document ..... I got only information which would be of my use .... like, I went through some example C program along with pin description and I have also studied how to add an external oscillator.

Download Code Download All Files

Group work - Embedded Programming

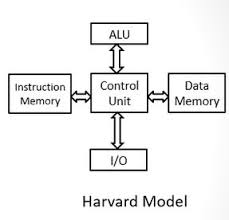

Harvard architecture

Memory

Applications and features of Harvard Architectures

Von Neumann Architecture